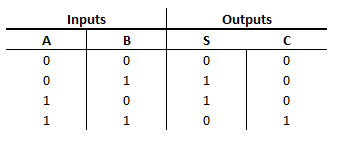

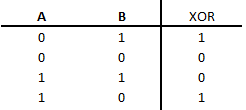

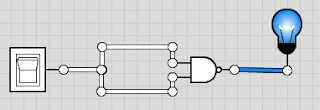

Los circuitos están realizados con logic.ly por si queréis probarlos, es una demo online que se puede abrir en el navegador de Internet de cualquier sistema operativo. Sumador Empecemos con el half-adder y despúes con el Full-adder. (La diferencia entre ellos es que en uno ya puedes sumar llevando) Half-adder Tabla de verdad S es resultado de la suma binaria, y C es el carry (la que te llevas) Circuito Full-adder Tabla de verdad Cin es la que te llevas, en el circuito hay que encencer Cin de forma manual para así poder verlo con más calma. Circuito Restadores Al igual que con la suma existe el half-subtractor y el full-subtractor. Half-Subtractor Tabla Circuito Full-subtractor Tabla Circuito Tanto al sumador como al restador los podemos hacer tan grandes como nosotros consideremos competente, estos ejemplos están realizados con la suma/resta de un bit, pero se puede hacer con los bits que nosotros queramos, tan solo...